http://www.dgyuezhen.comTSV技术持续突破 3D IC成本效益显著提升

SPTS营销副总裁David Butler则着眼于利用优化硅穿孔露出步骤,尽可能地使CMP步骤减至最少。根据Butler指出,SPTS已经开发出“深反应离子蚀刻(DRIE)” 设备,能够实现高达4.7μm/mn的蚀刻速率与±3.0%的均匀度,比竞争设备的蚀刻速率更快两倍,同时也较湿式蚀刻途径更快4倍。

精确硅穿孔露出

另一项重要的进展是SPTS的ReVia原位穿孔露出端点侦测技术。该自动光学分析系统以红外线(IR)干涉测量法为基础,侦测正在晶圆表面进行蚀刻的一组穿孔,并能在侦测到硅穿孔尖端出现时,停止硅穿孔露出工艺,从而实现仅高于表面1μm的均匀露出高度。

这将有助于避免昂贵的重复作业、硅穿孔未完全露出时必须进行更多的蚀刻作业,或是晶圆过度蚀刻造成的量产议题等。该公司还为蚀刻作业建置了双重来源调 整,让设备能以放射状在整个晶圆上严密控制蚀刻过程。这可在进行晶圆削薄步骤后,用于补偿芯片厚度变异。最后,SPTS还介绍其下一代蚀刻设备 Rapier XE,能够以完全可调整的放射状方式实现高达9μm/mn的蚀刻速率,可望提高4倍的生产力。

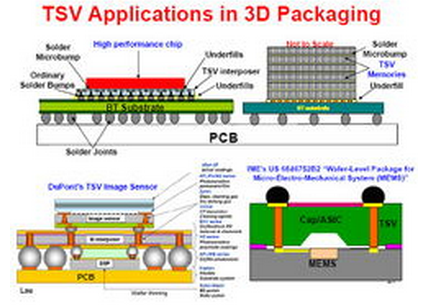

从制造商的立场来看,除非实现硅穿孔(TSV)所增加的成本以及随之而来的所有工艺步骤都能够因为芯片性能优势而得到大部分的补偿,或是工艺与材料成本大幅降低,才可能加速3D IC的量产。

因此,在今年初于法国举行的欧洲3D TSV高峰会上,提到一个重要的问题是,如何才能将拥有成本平均分配到整个供应链?

该由谁来制造TSV?

针对非MEMS IC,TSV也必须进一步微缩,这是因为如果你的TSV“排除区域”(Keep-out zone)耗用太多优质芯片面积的话,进展到下一代节点也并不一定有意义。由于这些工艺需要的设备组合通常只在晶圆厂中才有,因此TSV的整合理想上应该 由代工厂来完成,不过委外半导体组装与测试(OSAT)服务供货商也有机会在某种程度上参与。此外,有些电路板(PCB)制造商也考虑在PCB基板中嵌入 芯片,以主动硅中介层的形式实现2.5D整合。

除了当前经济环境可能限制TSV在短期内量产,市调公司Gartner首席产业分析师 Mark Stromberg预期,TSV市场还将面临资金成本议题,从而限制了有能力建置这项技术的业者数量。这主要来自于增加的资本与材料成本,以及越来越多的 工艺步骤。“在过渡到10nm节点时,系统设计将需要利用TSV技术,”不过,Stromberg强调,届时将会因为需要的庞大资本支出而减缓市场上仅存 几家主导IDM、代工厂以及一线半导体封装测试服务(SATS)供货商之间的市场竞争。

Silver进一步指出:“在代工厂、OSAT和IDM竞相抢占510亿美元的芯片组装与测试市场之际,预计未来将会看到更多的并购发生。随着封装技术变得越来越先进,特别是在晶圆级,前端工艺与后端封装之间将会发生重新整并与融合。”

台积电(TSMC)泛欧地区(EMEA)副总裁Miekei Ieong介绍该公司的CoWoS(芯片-晶圆-基板)整合型芯片服务,利用次微米级硅中介层以TSV技术将多个芯片整合于单一封装中。该公司可提供 CoWoS量产同质组件,并表示已经展示了异质CoWoS。该512bit Wide I/O DRAM测试芯片作业于200MHz核心频率,在全速作业模式时甚至可过载高达285MHz。

图1:台积电通过CoWos技术以28HPM工艺量产异质3D IC

“我们的1024bit CoWoS DRAM可驱动至1GHz,支持达128GB/s的频带,”Ieong表示,该公司并计划在今年第四季以前量产菊链式连接6颗芯片的高带宽内存。

针对较大的CoWoS组件,台积电已在60×60mm的基板上展示了26×48mm的硅中介层。该公司表示在28nm逻辑芯片上堆栈内存已经准备就绪,也为客户的测试载具设计与功能性验证规划了TSV设计规则。

Global Foundries负责封装技术研发的Michael Thiele透露,该公司已在纽约州Malta的Fab 8厂安装好TSV产线了,能以TSV为20nm器件以及未来的14nm器件特性进行整合。该公司同时也在其于新加坡的Fab 7厂安装300mm TSV产线,用于制造硅中介层,以及在德国Dresden的Fab 1厂增加以TSV整合28nm器件特性。

“在考虑2.5D产品量产时,客户通常期望代工厂能提出具代表性的测试载具及其所提供的系统级量化数据,”因此,Thiele表示Global Foundries为此采取双管齐下的途径,一方面利用可共享研发细节的外部测试载具,另一方面也建立自家的内部测试载具。

因此,该公司同时透过OSAT合作伙伴以及自家公司内部开发硅中介层与微柱互连。但是,Thiele强调,良率不足以及供应链延迟,都可能中止该技术应 用,特别是如果未能在供应链中清楚定义出产量的所有权分配。针对雷射钻孔与填充TSV穿孔、暂时性晶圆键合与去键合,以及硅穿孔露出等关键制程步骤进一步 降低成本,是3D IC得以落实大众市场的另一个必备条件。

降低材料与工艺成本

新加坡科技研究局旗下微电子研究 院(A-star Institute of Microelectronics;IME)产业开发总监Surya Bhattacharya则认为“后端工艺”(BEOL)与薄晶圆处理(包括暂时性晶圆键合与去键合-TBDB),才是3D IC组件的真正成本问题。他估计,由此所增加的工艺本身就占掉整体器件总成本的一半左右。

Bhattacharya大幅削减成本的方 法在于利用厚光电介质(聚合物)中的低成本多层铜线路重布电镀(Cu RDL),它仅需使用更少的工艺步骤,省略了CMP步骤与电介质蚀刻。IME已经开发出光阻材料,同时展示针对5/5μm与3/3μm等不同线宽与间距的 Cu RDL制造以及介电层之间的三个金属层。

铜线路重布电镀层具有3μm线宽与6μm聚合物间距,能够在10mm互连导线上支持 20Gbit/s信号,相形之下,采用镶嵌结构的昂贵1μm线宽铜线路,在4μm间距时只能支持7.5Gbit/s。IME还尝试在聚合物中采用2μm细 铜导线,计划在2016年以前实现0.5μm线宽,以持续其与先进TSV的竞争力。

Bhattacharya透露,这种方法最重要的是利用“无载片(carrier-less)”技术,以避免或减少TBDB步骤;在芯片到晶圆键合与缝隙填充之后,整个晶圆由于背侧硅穿孔露出而进行覆盖成型与翻转,并直接由环氧模型树脂(EMC)维持。

总之,移除后端的Cu RDL沈积工艺与TBDB步骤后,Bhattacharya粗估,这种晶圆级工艺的成本可大幅削减40%~50%。

美商应用材料(Applied Materials)硅系统事业群封装技术与先进产品技术开发管理总监Sesh Ramaswami认同这一工艺,并表示,“从铜镶嵌结构过渡到在有机层上实现Cu RDL,则可以减少约15%至20%的工艺成本。”

缩短冗长又昂贵的CMP工艺方法之一在于调整这种硅穿孔的生长及随之而来的硅穿孔露出步骤,以便在硅穿孔露出时停止蚀刻,使CMP期间仅需移除很少材料,以开启与修整硅穿孔至晶圆表面。

Tel Nexx工艺技术总监Steve Golovato则针对利用适形阻障-晶种(barrier-seed)层沈积的高深宽比TSV建置进行拥有成本分析。相较于利用离子化物理气相沈积 (I-PVD)阻障-晶种层沈积方式可能导致材料在硅穿孔上造成过度负担(而需要进行更多CMP加以移除),Golovato表示,业界可以利用这种特殊 的TSV填充来限制CMP的成本。

I-PVD阻障-晶种层沈积 完美的适形阻障-晶种层沈积

更有趣的是,Golovato预计,该公司的无电解铜适形阻障-晶种层沈积技术的TSV深宽比约20,可在晶圆级时实现比I-PVD更低50%的成本。